Now Reading: EUV vs. High-NA EUV: What’s the Difference and Why It Matters for the Future of Chips

- 01

EUV vs. High-NA EUV: What’s the Difference and Why It Matters for the Future of Chips

EUV vs. High-NA EUV: What’s the Difference and Why It Matters for the Future of Chips

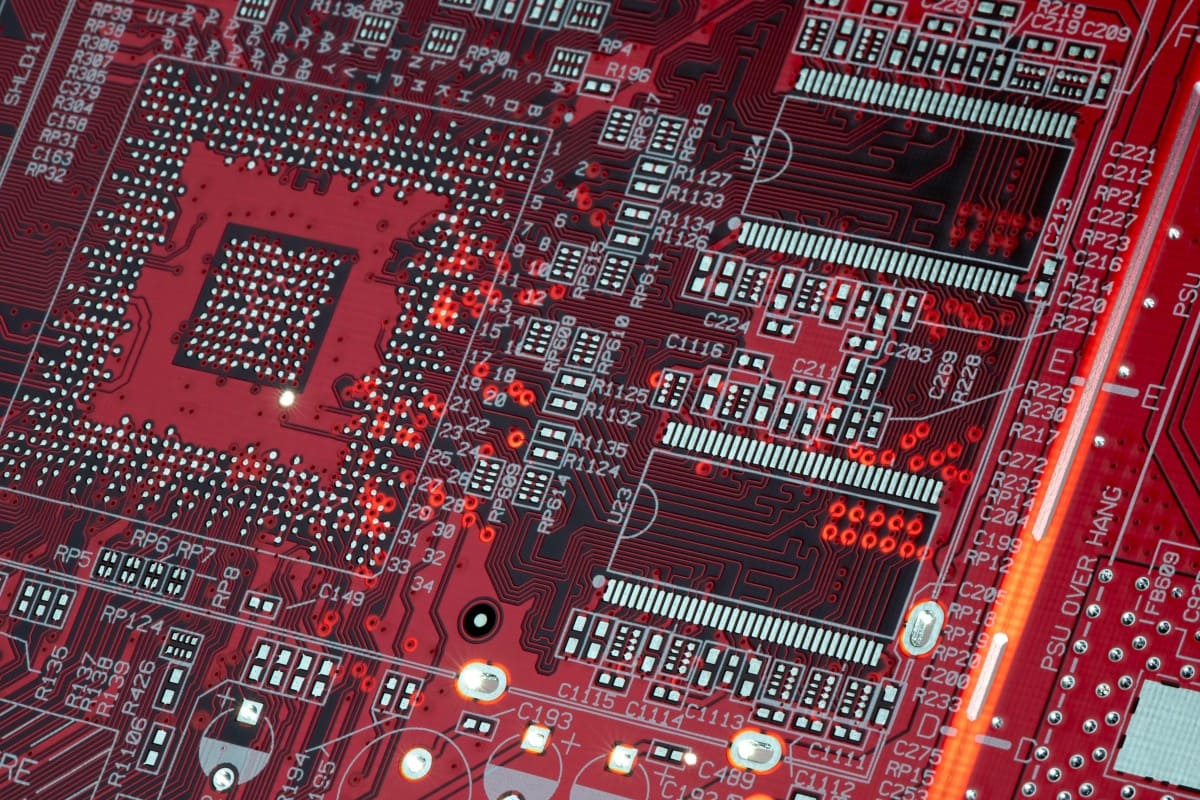

As the semiconductor industry races toward 2nm process technology, traditional EUV lithography faces physical limits in patterning ever-smaller transistors. High-NA EUV lithography emerges as the game-changing solution, offering higher resolution, improved yield, and the capability to power next-generation chips for AI, HPC, and mobile devices. This article explores the differences between EUV and High-NA EUV, the science behind advanced optics, the global adoption race led by ASML, Intel, TSMC, and Samsung, and why High-NA EUV is critical for shaping the future of chipmaking.

Introduction

In the relentless pursuit of Moore’s Law, the semiconductor industry has continually pushed the boundaries of technology, striving to pack more transistors into ever-smaller chip designs. Extreme Ultraviolet (EUV) lithography revolutionized this quest, enabling nodes previously thought unattainable. However, as we approach the 2nm process technology era, conventional EUV begins to encounter physical and practical limitations. Enter High-NA EUV lithography — a breakthrough innovation poised to redefine next-gen chip manufacturing.

High-NA EUV isn’t merely an incremental upgrade; it represents a fundamental leap in advanced lithography capabilities. By enhancing resolution, improving process efficiency, and supporting intricate designs, it promises to shape the future of chipmaking, powering innovations in AI, HPC, mobile devices, and edge computing. This blog delves into the critical differences between EUV and High-NA EUV, the science behind the technology, industry implications, and why semiconductor leaders are racing to adopt it globally.

What Is High-NA EUV Lithography?

High-NA EUV lithography is an advanced version of conventional EUV technology. While standard EUV systems operate with a numerical aperture (NA) of approximately 0.33, High-NA EUV increases this value to roughly 0.55, allowing for finer feature resolution. In practical terms, this enables chipmakers to print extremely small transistor features, reducing the need for multiple patterning steps and ultimately improving yield.

High-NA EUV systems utilize larger projection optics, refined mirrors, and enhanced illumination strategies to achieve unprecedented precision. These capabilities are critical for fabricating 2nm nodes and beyond, supporting both logic and memory devices. The technology is not only pivotal for maintaining Moore’s Law but also for delivering performance gains in high-demand applications like AI processors and data center accelerators.

How It Differs from Traditional EUV

While both EUV and High-NA EUV use 13.5nm wavelength light, several key differences define their capabilities:

Numerical Aperture (NA): Traditional EUV uses NA ~0.33, while High-NA EUV reaches ~0.55, increasing resolution and pattern fidelity.

Resolution & Feature Size: High-NA EUV can resolve sub-8nm features in single exposure, whereas standard EUV may require multiple patterning steps.

Depth of Focus: Higher NA reduces depth of focus, necessitating thinner resist layers and tighter process controls.

Optical Complexity: High-NA systems demand larger and more precise optics, increasing system size, weight, and engineering challenges.

Patterning Efficiency: By reducing the number of required exposures, High-NA EUV lowers manufacturing complexity and can improve yield despite higher initial equipment costs.

The Science Behind High-NA (Numerical Aperture & Optics)

Understanding High-NA EUV begins with numerical aperture, a critical optical parameter that defines a system’s ability to resolve small features. Higher NA allows the system to capture more diffracted light from the mask, enabling finer detail reproduction on the wafer.

Key Principles:

Rayleigh Equation: Resolution ≈ k₁ × (λ / NA). Increasing NA directly improves resolution, assuming other factors remain constant.

Optical Aberrations: As NA increases, lens and mirror distortions, flare, and shadowing effects become more pronounced, requiring precise corrective measures.

Lens & Mirror Demands: High-NA EUV optics are larger, heavier, and demand extreme surface precision.

Stitching & Field Size: High-NA optics cover smaller fields, making large die patterning more complex and necessitating careful stitching to maintain alignment and overlay accuracy.

These optical enhancements make High-NA EUV a marvel of engineering, pushing the boundaries of what is possible in semiconductor innovation.

Why High-NA EUV Is Critical for the Future of Chipmaking

The semiconductor industry is approaching physical limits where traditional EUV struggles:

2nm and Beyond: Standard EUV cannot reliably pattern critical features at these scales without multi-patterning, which increases cost and complexity.

Efficiency Gains: High-NA EUV reduces exposure steps and mask usage, potentially lowering production cost per chip over time.

Performance Enhancements: Smaller features lead to reduced parasitic resistance and capacitance, improving power efficiency and performance.

Moore’s Law Continuation: High-NA EUV offers a path to keep transistor scaling viable, extending the benefits of Moore’s Law into the next decade.

ASML and the Global Race Toward High-NA

ASML, the Netherlands-based lithography giant, leads the development of High-NA EUV systems. Collaborating with ZEISS, ASML has created precision optics and illumination systems capable of meeting the stringent demands of advanced lithography.

Key points:

EXE Platform: ASML’s High-NA EUV machines are among the most complex instruments ever built, with projections for volume production in the mid-2020s.

Global Competition: Semiconductor manufacturers worldwide are racing to adopt High-NA systems to maintain technological leadership.

Supply Chain Collaboration: High-NA EUV requires co-development with optics, materials, and metrology partners to ensure reliability and yield.

Impact on Semiconductor Leaders (Intel, TSMC, Samsung)

High-NA EUV adoption is poised to reshape the competitive landscape:

Intel: First to receive and test High-NA EUV systems, targeting the 14A node and beyond, ensuring leadership in logic process technology.

TSMC: Evaluating adoption carefully; may use High-NA selectively for critical layers at 1.4nm class nodes.

Samsung: Strong interest in integrating High-NA for advanced memory and logic fabrication, accelerating performance improvements.

Memory Manufacturers: SK hynix has announced plans to leverage High-NA EUV for mass production, signaling a broader industry adoption trend.

Challenges and Limitations of High-NA EUV

Despite its potential, High-NA EUV faces significant hurdles:

High Cost: Machines cost hundreds of millions, requiring significant capital expenditure.

Throughput & Yield: Tighter process margins and complex optics may reduce throughput compared to traditional EUV.

Resist Limitations: Thinner resist layers increase stochastic defects and line-edge roughness.

Mask Complexity: Requires ultra-high precision masks and overlay accuracy.

Field Stitching: Smaller optical fields demand meticulous stitching for large die fabrication.

Ecosystem Readiness: Computational lithography, metrology, and materials must evolve alongside High-NA adoption.

The Role of High-NA in AI, 2nm, and Next-Gen Technologies

The AI revolution and next-generation devices are driving chip demand at unprecedented scales:

AI Accelerators: High transistor density reduces energy consumption per operation, critical for AI workloads.

2nm Process Technology: Enables ultra-dense logic and memory devices for high-performance computing.

Edge Devices & IoT: Efficient, smaller chips extend battery life and enhance performance in portable electronics.

Data Centers: High-NA EUV supports faster, more energy-efficient processors, meeting the needs of cloud and HPC infrastructure.

The Future of Semiconductor Manufacturing

High-NA EUV represents a stepping stone to future lithography breakthroughs:

Hyper-NA Development: Optical systems with NA > 0.55 may push resolution even further.

Alternative Techniques: B-EUV, soft X-ray lithography, and nanoimprint techniques are being explored for beyond 2nm.

Computational Lithography: AI-assisted modeling and process optimization will complement High-NA adoption.

Hybrid Manufacturing Strategies: Chipmakers may combine conventional EUV and High-NA selectively to optimize cost and efficiency.

The next decade will likely witness a hybrid landscape, balancing technological capability, cost, and volume production feasibility.

Conclusion – Why High-NA EUV Defines the Next Decade of Innovation

High-NA EUV is more than an incremental upgrade — it is a foundational technology for the next generation of semiconductor devices. By resolving the challenges of conventional EUV, it enables smaller, faster, and more efficient chips, supporting AI, HPC, mobile, and IoT innovations. The global race to adopt High-NA EUV underscores its strategic importance. For engineers, researchers, and industry stakeholders, understanding and embracing High-NA is crucial for shaping the future of chipmaking.

FAQs

What is the difference between EUV and High-NA EUV?

EUV uses ~0.33 NA optics; High-NA EUV uses ~0.55 NA, allowing finer resolution and fewer patterning steps.Why can’t standard EUV handle 2nm nodes alone?

Standard EUV reaches its resolution limits, requiring complex multi-patterning to achieve sub-2nm features.What does numerical aperture (NA) mean?

NA measures an optical system’s ability to capture diffracted light; higher NA improves resolution.Will High-NA EUV reduce chip manufacturing costs?

It can lower patterning steps but requires expensive equipment and infrastructure, balancing cost gains over time.Which companies are leading in High-NA adoption?

Intel, Samsung, and memory firms like SK hynix are early adopters; TSMC is evaluating selective implementation.What technical challenges does High-NA EUV face?

Throughput, yield, resist stochastic defects, mask complexity, optics precision, and field stitching are key challenges.Can High-NA EUV completely replace traditional EUV?

Likely not immediately; hybrid usage is expected where critical layers utilize High-NA.How does High-NA EUV support AI chip development?

It allows denser, more energy-efficient designs crucial for AI accelerators and high-performance computing.What is Hyper-NA EUV?

Hyper-NA refers to future lithography with NA > 0.55, promising even higher resolution but greater complexity.When will High-NA EUV reach mass production?

Industry forecasts suggest ramp-up between 2025–2030, depending on yield, infrastructure, and cost factors.